DesignWare 112G Ethernet PHY IP Insertion Loss Compensation Capability | DesignWare 112G 以太网 PHY IP 插损补偿能力

5:25

描述

相关视频

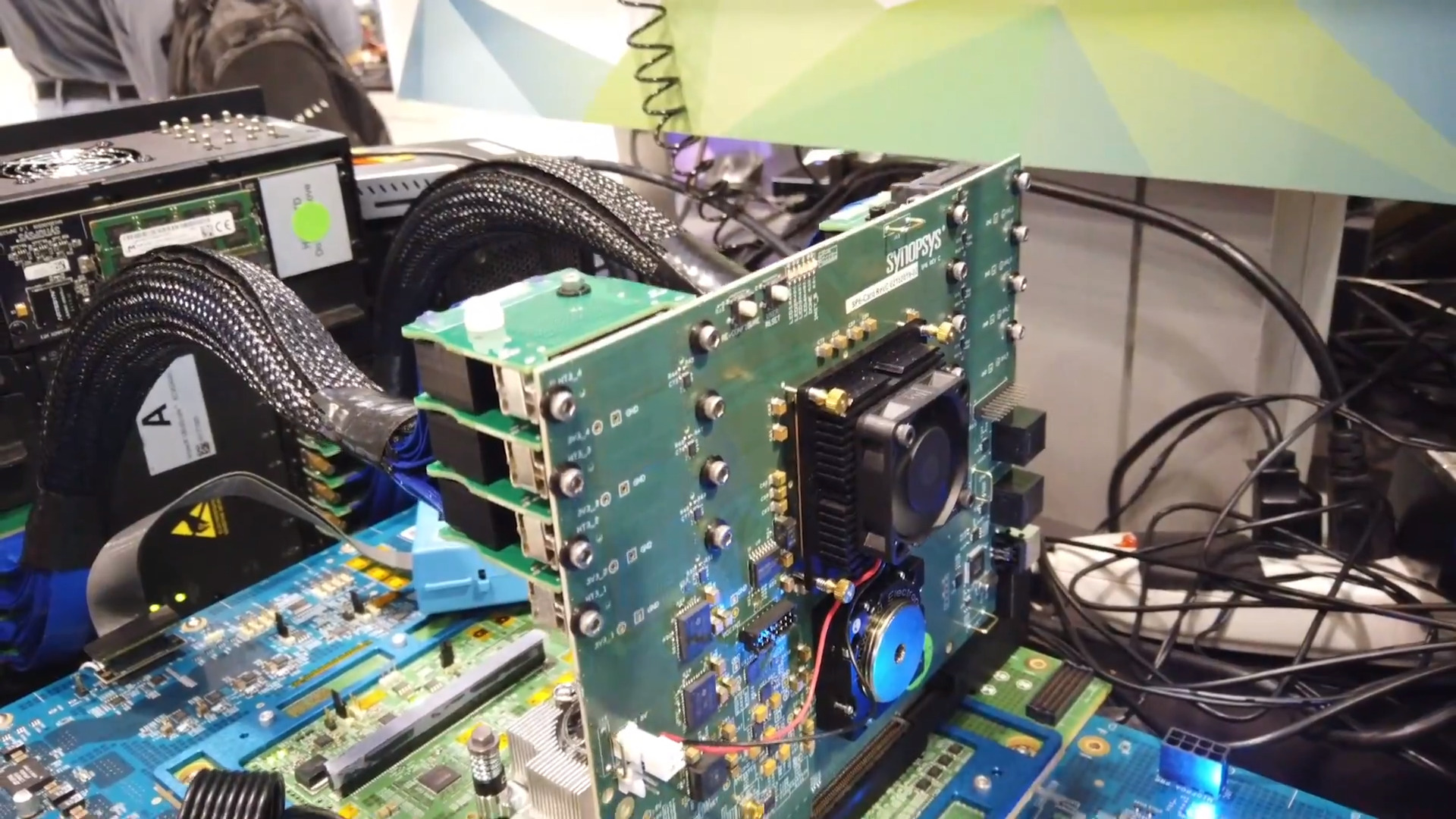

新思科技112G PHY 接收器在不同数量通道插入损耗下的性能。该IP 达到了各项标准的要求,支持FinFET工艺的一系列节点,具有领先的功耗、性能和面积,适用于高性能计算SoC芯片。

查看更多

查看更少